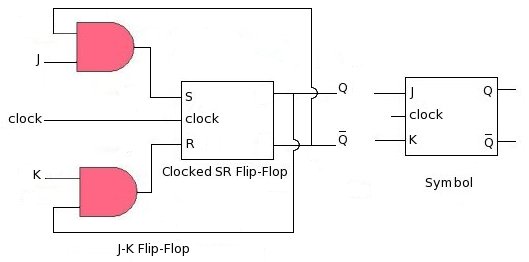

We observed that in SR flip-flop, input R=1 & S=1 leads flip-flops to an unpredictable state. The SR flip flop circuit can be modified so that if both the inputs are 1, then also the output is predictable.

Behavior of the circuit is shown in the table below...

| J | K | Q(t) | Q(t + 1) |

| 0 | 0 | 0 -> | 0 |

| 0 | 0 | 1 -> | 1 |

| 0 | 1 | 0 -> | 0 |

| 0 | 1 | 1 -> | 0 |

| 1 | 0 | 0 -> | 1 |

| 1 | 0 | 1 -> | 1 |

| 1 | 1 | 0 -> | 1 |

| 1 | 1 | 1 -> | 0 |

Here also, note that clock is required. The output will change only

while the clock is '1', and while clock is '0' all inputs will be

ignored.