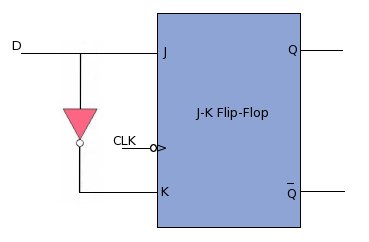

This is basically derived from J-K (master-slave) flip-flop, where J and K are connected together with a NOT gate as shown in the diagram below. This has only one input called as D. Since J-K master-slave is used, this flip-flop is clock edge triggered and works on clock edge.

|

Input Dn |

Output Qn+1 |

| 0 | 0 |

| 1 | 1 |

In D flip-flop the input data at D appears at the output only after next

clock edge (-ve edge). Thus the transfer of the data from the input to

the output is delayed by one clock, hence the name delay(D) Flip-flop.

The D-type flip-flops are very much used in delay-chains for pipe-line

adjustments.